1. Overview¶

This document describes the various open-source Interconnect IPs available by InCore Semiconductors. A majority of the IPs are designed in Bluespec System Verilog (BSV). Currently only a subset of AMBA ® (Advanced Microntroller Bus Architecture) protocol implementations are available.

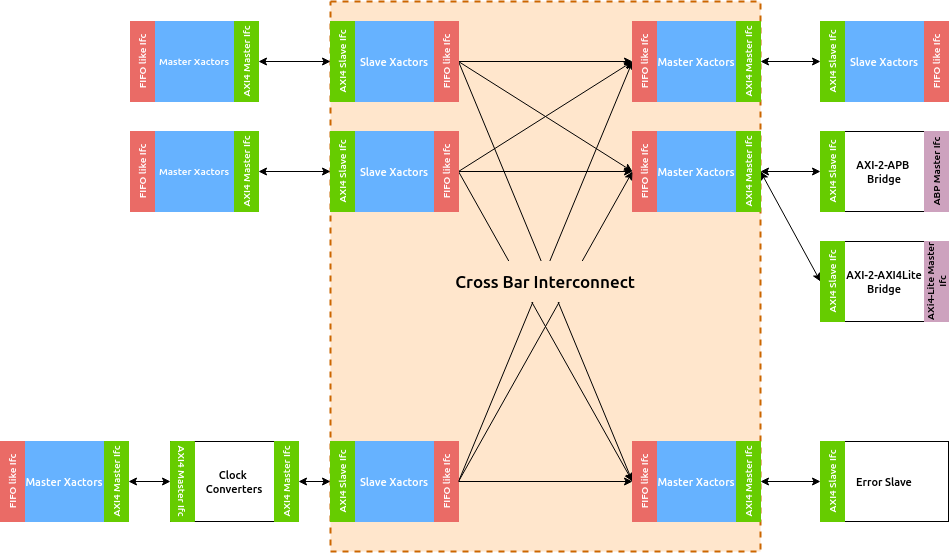

The Interconnect IP subsystem comprises of multiple blocks each of which can be used independently in external designs. The following is an overview of these components:

- AXI4 ™ Cross-bar Interconnect : Connects one or more AXI4 compliant masters to one or more memory mapped slaves.

- AXI4-Lite ™ Cross-bar Interconnect : Connects one or more AXI4-Lite compliant masters to one or more memory mapped slaves.

- APB Interconnect : Connects one APB compliant master to one or more memory mapped slaves.

- Protocol Bridges : connects AXI4 master to an AXI4-Lite or an APB slave

- Buffers: connects an AXI4/AXI4Lite master to another AXI4/AXI4Lite memory mapped slave through a set of pipelined registers, typically used to break a critical path

- Error Slave: A dummy slave to respond with error for every request type.

Fig. 1.1 Block level representation of various AXI4 IP components

Fig. 1.1 provides a block level representation of how the above IP blocks can possibly interact with each other.